Fetch-Decode-Execute.ppt

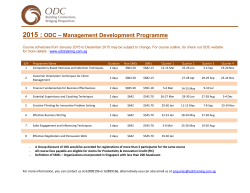

Modern computers use the stored program concept. The stored program concept is that: o machine code instructions are stored in main memory, o these are fetched and executed serially, o by a processor that performs arithmetic and logical operations. The concept was introduced by John von Neumann. Previously, “programs” were entered into a computer by techniques such as setting switches and plugging patch leads into panels. The concept can be seen earlier in Alan Turing’s development of the Universal Turing Machine. Machine Architecture Machine Architecture The Fetch-Execute cycle is the basic operation cycle of a computer. The cycle is repeated over and over again from the moment a computer is turned on until it is turned off. Each time that the cycle is iterated, a single machine code instruction if fetched from main memory, decoded and executed. The result (output) of an instruction is usually stored into a general purpose register but could also be written back to main memory. Machine Architecture The Fetch-Execute cycle has three stages: 1. Fetch: The instruction to execute is retrieved from the main memory. 2. Decode: The op-code part of the instruction is examined to determine which parts of the CPU must be used to carry out the instruction. 3. Execute: The appropriate hardware components of the CPU are used to carry out the instruction. Machine Architecture The Fetch-Execute cycle makes use of some specific purpose registers on the processor: o Program Counter (PC): Stores the address in main memory of the next instruction to execute. o Memory Address Register (MAR): Stores the address in main memory of the location that the processor is currently reading data from or writing data to. o Memory Buffer Register (MBR): Temporarily stores the word of data that is currently being transferred between the processor and the main memory. o Current Instruction Register (CIR): Stores the instruction that is currently being executed by the processor whilst it is decoded and executed. Machine Architecture The steps involved in the Fetch-Execute cycle are often described in register transfer notation. This has the format: Register / Storage Location Value e.g. MAR [PC] means that the contents of the Program Counter are copied into the Memory Address Register The symbols [] are used to indicate the contents or a register or storage location. Machine Architecture The animation on the next slide shows one iteration of the fetch-execute cycle, to carry out the instruction stored in memory location 104. The animation focuses in most detail on the fetch stage of the cycle as this stage is the same for all instructions. Machine Architecture 1 MAR [PC] (Contents of Program Counter transferred to MAR) 2 (a) PC [PC] + 1 (Increment contents of Program Counter) (b) MBR [Memory]addressed (Contents of addressed memory location loaded into MBR) 3 • Memory address transferred along address bus to main CIR [MBR] memory. (Transfer contents of • Contents of addressed location looked up in main memory. Memory Buffer Register • Looked up value transferred to processor along data bus. into Current Instruction Register) Processor Main Memory 4 Decode instruction 5 Execute instruction Machine Architecture +1 Simultaneous PC MAR 104 105 104 104 CIR MBR Data Bus 10000101 10000101 10000101 Address Bus Address Content 100 101 102 103 104 105 106 01110101 11010101 00101000 11011001 10000101 10101101 01001101 During the decode stage, the control unit splits the instruction in the CIR into two parts: instruction 10000101 1000 0101 op-code operand Op-code: The binary pattern which identifies the instruction to be carried out e.g. add, or, branch. Operand: The data that the instruction will operate on. Machine Architecture The operand could be a number such as 5, which the instruction should use directly. Alternatively it might be the address in main memory where the data to use is stored. How to interpret the operand will depend upon the addressing mode that the instruction is using. Instructions may have zero, one or more operands. Machine Architecture What happens in the execute stage of the cycle is determined by the op-code of the instruction that is being executed. The op-code will determine which circuitry within the processor should be used to carry out the instruction. Temporary results and the final result of executing instructions are usually stored in registers instead of main memory as registers can be accessed much more quickly. Modern computers have many general purpose registers, but it can be convenient to think of a simplified model of a computer with just one general purpose register, known as the accumulator. Machine Architecture The example below shows the execute stage for an ADD instruction that adds the value in a specified memory location onto the current value in the accumulator register, storing the result in the accumulator. Action Explanation MAR [CIR (Operand)] Transfer the value in the instruction’s operand into the MAR. This is the address that the value to add on is stored at. MBR [Memory]addressed Fetch the value to add from main memory into the MBR. ALU MBR, [ACC] In the ALU, add together the contents of the MBR and the accumulator. ACC [ALU] Write the output of the instruction into the accumulator. Machine Architecture After an instruction has been executed, the contents of a special purpose register known as the status register are updated. Each bit of the status register is known as a flag and has a specific purpose. Some example status register bits are: Bit Purpose Carry Set if the last instruction produced a carry. Zero Set if the last instruction produced a result of zero. Overflow Set if the last instruction produced an overflow, i.e. a result outside the allowable range. The status register stores information about the result of previous operations as these may affect future operations. Machine Architecture

© Copyright 2025